- 1:一、UART

- 2:二、IIC 总线

- 3:三、SPI总线

- 4:四、CAN总线

- 4.1:LIN总线:

通信总线协议学习整理Tinus Chen

一、UART

UART是一个大家族,其包括了RS232、RS499、RS423、RS422和RS485等接口标准规范和总线标准规范。它们的主要区别在于其各自的电平范围不相同。

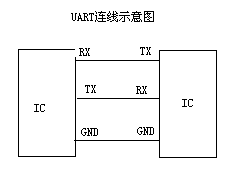

嵌入式设备中常常使用到的是TTL、TTL转RS232的这种方式。常用的就三根引线:发送线TX、接收线RX、电平参考地线GND。

1.1 电路示意图

1.2 通信协议

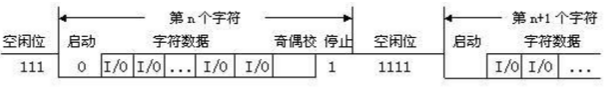

将传输数据的每个字符一位接一位地传输。

起始位:先发出一个逻辑”0”的信号,表示传输字符的开始。

数据位:紧接着起始位之后。数据位的个数可以是4、5、6、7、8等,构成一个字符。通常采用ASCII码。

奇偶校验位:数据位加上这一位后,使得“1”的位数应为偶数(偶校验)或奇数(奇校验),以此来校验资料传送的正确性。

停止位:它是一个字符数据的结束标志。可以是1位、1.5位、2位的高电平。

空闲位:处于逻辑“1”状态,表示当前线路上没有资料传送。

波特率:数据传输的速率。有以下几个档位:300、600、1200、2400、4800、9600、19200、38400、43000、56000、57600、115200.当然也可以自定义。在数据传输和接收双方,需要预先统一波特率,以便正确的传输数据。

二、IIC 总线

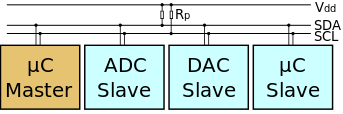

I²C (Inter-Integrated Circuit)。其拥有一根数据线SDA和一根时钟线SCL。其总线通过上拉电阻与电源相连接。每个接到I2C总线上的器件都有唯一的地址。其中,主动发起操作的一方为主机,另外一方为从机。

1.1 电路示意图

1.2 数据传输

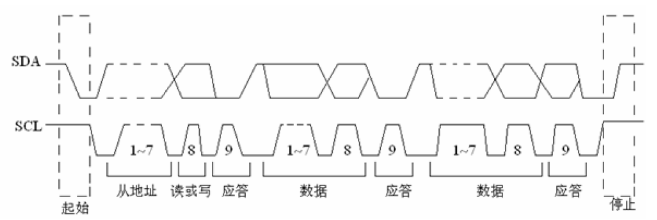

当没有数据传输的时候,两根总线都为高电平;当采集IIC上的数据时,其时钟线SCL必须是高电平且SDA的数据必须保持稳定不变---将SDA的电平与SCL的高电平进行“与”操作后,以便确定SDA上是1还是0;在SCL为低电平的时候,SDA上的数据可以进行跳变。

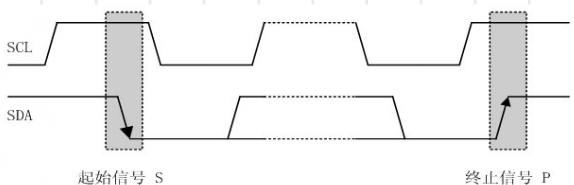

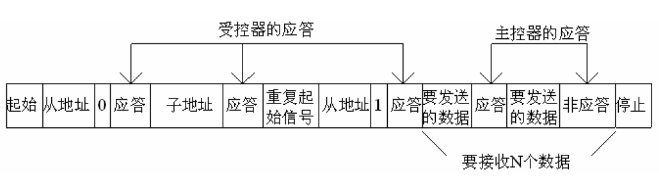

数据传输开始时,需要发送一个起始信号;数据传输结束后,需要发送一个终止信号;每8bit数据传输结束,都需要一个ACK。起止信号都有Master发出,而ACK则可能由Master或者SLAVE来发出。数据的传输采用大端传输。

开始信号:SCL为高电平,SDA的电平由高跳到低表示开始信号。

终止信号:SCL为高电平,SDA的电平由低跳到高表示终止信号。

1.3 数据协议

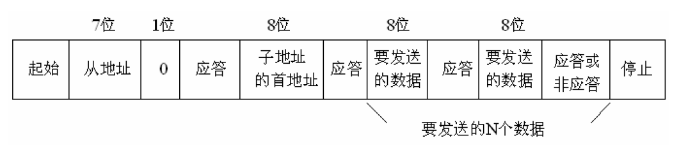

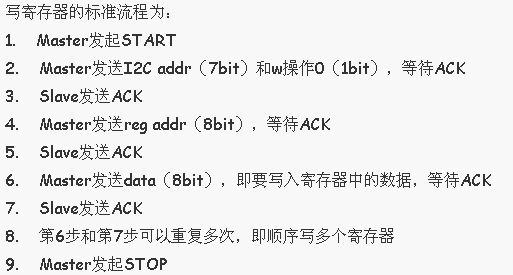

1.4 I2C读写流程

参考:

http://dpinglee.blog.163.com/blog/static/14409775320112239374615

https://en.wikipedia.org/wiki/I%C2%B2C

http://wenku.baidu.com/view/7c310976f46527d3240ce0e5

http://wenku.baidu.com/view/bdb46aa60029bd64783e2c6f

三、SPI总线

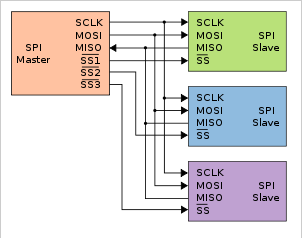

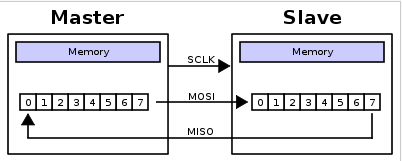

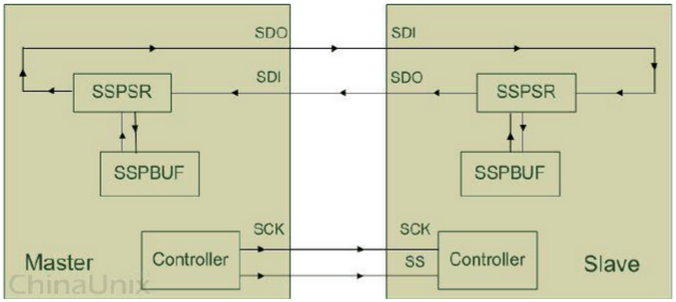

SPI(Serial Peripheral Interface)是一种串行串行同步通讯协议,由一个主设备和一个或多个从设备组成。其拥有四根(类)硬脚引线,分别为 SDI(串行数据输入),SDO(串行数据输出),SCK(串行移位时钟),CS(片选)。因为一个主设备可以挂多个从设备,则通过片选引脚对从设备进行选择。从设备的工作时钟则是来自于主设备的SCK线。

1.1 电路示意图

1.2 数据的传输

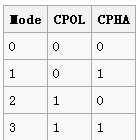

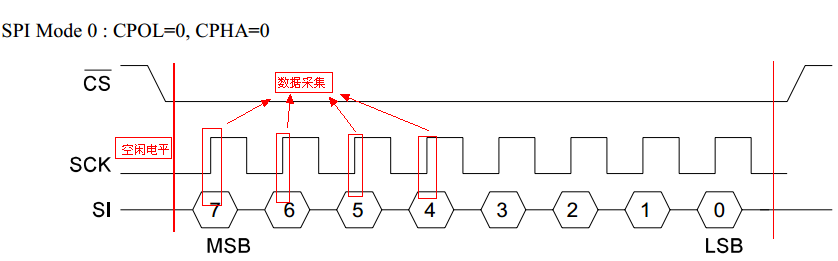

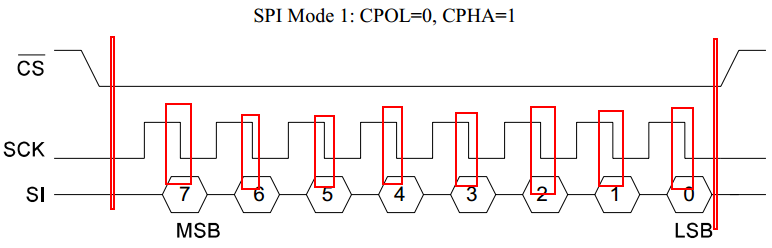

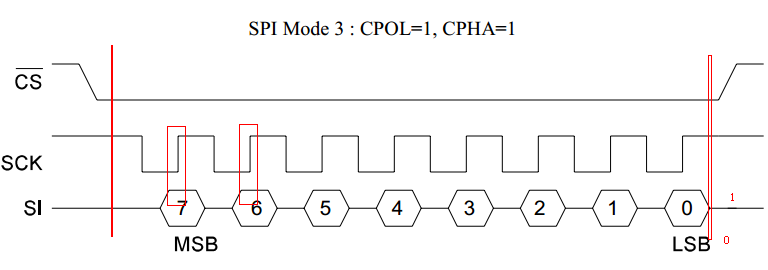

SPI在数据传输的时候,需要确定两件事情:其一,数据是在时钟的上升沿采集还是下降沿采集;其二,时钟的初始(空闲)状态是为高电平还是低电平。而I2C的空闲状态,时钟线为高电平;数据采集的时候,时钟线也为高电平。但SPI给出了更自由的方式。

CPOL:时钟极性, 表示 SPI 在空闲时, 时钟信号是高电平还是低电平。

CPHA:时钟相位, 表示 SPI 设备是在 SCK 管脚上的时钟信号变为上升沿时触发数据采样, 还是在时钟信号变为下降沿时触发数据采样。

那么,SPI CPOL有两种可能,CPHA有两种可能,则SPI数据传输就有四种可能---按照标准的说法,SPI数据传输就有四种模式。

1.3 SPI读写

SPI在硬件设计上采用的双数据线制,根据设计,在SPI通信过程中,主从设备之间会形成一个数据环形链路---也即是,主设备向从设备写一次数据,从设备就会回一次数据(至于该从设备回复的数据是否有效,则另当别论---如果有效,主设备就把它读入;如果无效,则丢弃即可)。

四、CAN总线

- 双线差分信号;(1Mbits<=40m);

- 多主站结构(协议对点的数量没有限制,正常最多110个);

- 每个报文的内容通过标识符辨别,网络中唯一;性

显性电平为逻辑0,因为线与的机制,0的时候表示了总线处于非空闲的状态,显性位覆盖隐性位;

NRZ编码方式-保证相同带宽的情况下,NRZ包含的信息量更大;

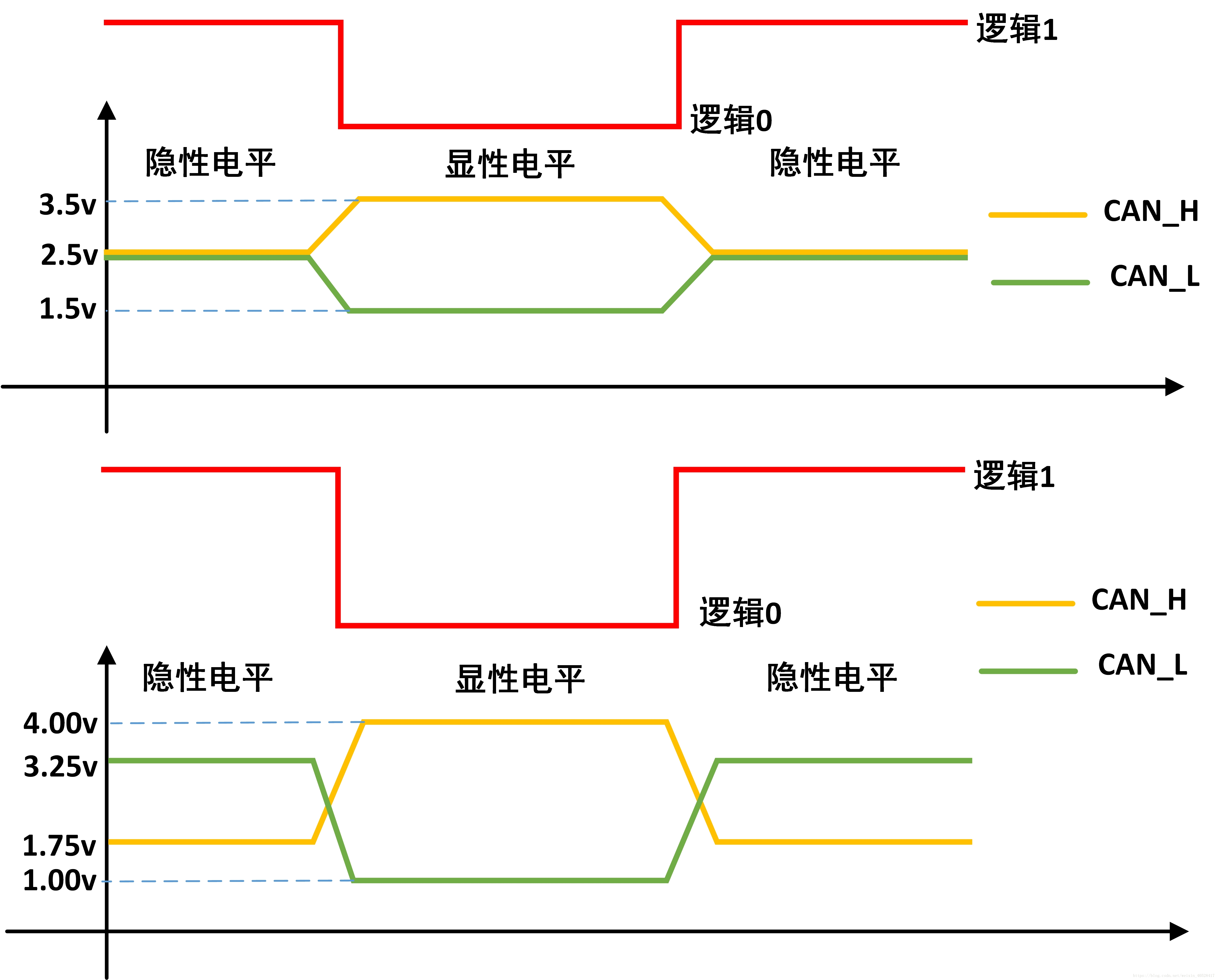

此图上为高速CAN(500k),下为低速容错CAN(125k);

高速CAN的容错性TJA1040:CAN_L对GND可以短路;

低速容错CANTJA1054:CAN_H和CAN_L可以分别开路短路;

?关于为什么汽车控制器很少有1M的CAN,从成本角度考虑,CAN收发器的成本会上升,此外500K足够使用了;

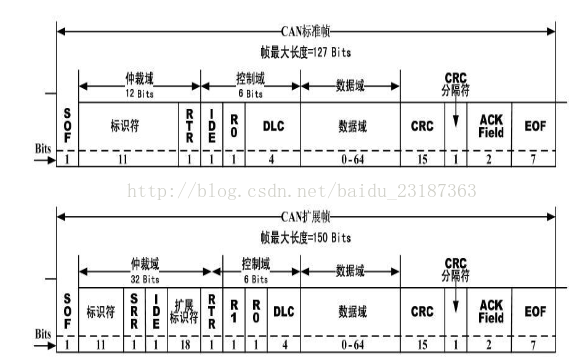

标准帧11位ID,扩展帧29位ID;

首位是SOF为一个显性位,逻辑0,用于数据同步;

DLC:数据长度码;

ACK:为了确保报文被至少一个节点正确接收,接收成功后置0,原本为1,回读为0后,确认被接收;

EOF:7干扰连续隐性位,表示数据结束,节点在检测到11个连续的隐性位后认为总线空闲;

数据链路层:

- 回读机制:总线空闲发送,发送过程中回读,判断发送位和回读位是否一致,即检测是否有别的节点发报文;

- 线与优先级:ID越小优先级越高;

- 非破坏性仲裁:并行的发送变成了串行的发送,这样的机制存在的一是一是因为在A优先级高先发送后,BCD可能会同时检测发送,此时需要检测排队;

- 接收多帧报文:过滤器-过滤到不要的ID;屏蔽-设置是否生效(不生效的位置,ID可变,可以检测多帧)

- NRZ编码,存储量更大,但是边沿变化少,所以引入位填充;

LIN总线:

6位ID;单主节点,多从节点,最多16个节点;(基于UART/SCI接口,节省成本)

20Kbit/s;

进度表:规定帧ID的传输次序;规定帧时隙;